Snoopy Bus Protocols Snoopy protocols achieve data consistency between the cache memory and the shared memory through a bus-based memory system. Write-invalidate and write-update policies are used for maintaining cache consistency.

What is the limitation of the snoopy protocol?

The disadvantage of bus snooping is limited scalability. Frequent snooping on a cache causes a race with an access from a processor, thus it can increase cache access time and power consumption. Each of the requests has to be broadcast to all nodes in a system.

What is CPU snoop mode?

Snooping is used to probe the content of cache on both local and remote processors to find the copy of requested data resides in any of caches. If NUMA is disabled (Node interleaving enabled in BIOS) then snoop mode is disabled automatically.

What is snooping cache coherence protocol?

Snooping maintains the consistency of caches in a multiprocessor. The snooping unit uses a MESI-style cache coherency protocol that categorizes each cache line as either modified, exclusive, shared, or invalid. Each CPU’s snooping unit looks at writes from other processors.What is the write through method?

Write through is a storage method in which data is written into the cache and the corresponding main memory location at the same time. The cached data allows for fast retrieval on demand, while the same data in main memory ensures that nothing will get lost if a crash, power failure, or other system disruption occurs.

What is the advantage of directory based protocols?

The important advantage of directory based protocols is that they scale much better than snoopy protocols. In addition to this it has the advantage of ability to exploit arbitrary point-to-point interconnects. But mean time it also has the overhead in terms of the storage and manipulation of directory state.

What is cache miss?

A cache miss is an event in which a system or application makes a request to retrieve data from a cache, but that specific data is not currently in cache memory. … A cache miss requires the system or application to make a second attempt to locate the data, this time against the slower main database.

What are the different types of snoopy protocol?

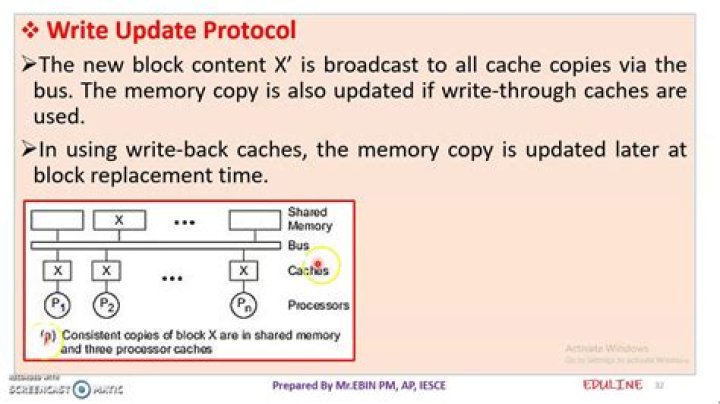

The two snooping protocol types are: Write-Invalidate: Before changing its copy, a data-writing processor invalidates copies of data in all other system processor caches. This action is communicated by an invalidation signal sent over the bus. Write-Update: A data-writing processor announces new data through the bus.Is cache a memory?

cache memory, also called cache, supplementary memory system that temporarily stores frequently used instructions and data for quicker processing by the central processing unit (CPU) of a computer. The cache augments, and is an extension of, a computer’s main memory.

What is the difference between cache coherence and memory consistency?Cache Coherence describes the behavior of reads and writes to the same memory location. Memory consistency describes the behavior of reads and writes in relation to other locations.

Article first time published onWhy do we need a cache coherence protocol?

In computer architecture, cache coherence is the uniformity of shared resource data that ends up stored in multiple local caches. When clients in a system maintain caches of a common memory resource, problems may arise with incoherent data, which is particularly the case with CPUs in a multiprocessing system.

How can the problem be solved with a snoopy cache controller?

Two basic approaches to the snoopy protocol have been explored: Write invalidates or write- update (write-broadcast) … When one of the caches wants to perform a write to the line it first issues a notice that invalidates that tine in the other caches, making the line exclusive to the writing cache.

What does a memory bus do?

The memory bus is a type of computer bus, usually in the form of a set of wires or conductors which connects electrical components and allow transfers of data and addresses from the main memory to the central processing unit (CPU) or a memory controller.

What is difference between write through and write back protocol?

In case of write-through mode data is written in cache and in source memory when it is modified. … Write-back mode means that data is written only in cache. And when it is being replaced in cache memory it is written in back in source memory. Then source memory is always written only once.

What is write through vs write back?

Write-through: Write is done synchronously both to the cache and to the backing store. Write-back (or Write-behind): Writing is done only to the cache. A modified cache block is written back to the store, just before it is replaced.

What is write hit in cache?

write hit means the page on which you want to write is present in cache, similiarly write miss page is when page on which write to be performed is not in cache. 2. 2.

What is L1 L2 and L3 cache?

L1 is usually part of the CPU chip itself and is both the smallest and the fastest to access. Its size is often restricted to between 8 KB and 64 KB. L2 and L3 caches are bigger than L1. They are extra caches built between the CPU and the RAM. … The more L2 and L3 memory available, the faster a computer can run.

What is L3 cache?

(Level 3 cache) A memory bank built onto the motherboard or within the CPU module. The L3 cache feeds the L2 cache, and its memory is typically slower than the L2 memory, but faster than main memory. The L3 cache feeds the L2 cache, which feeds the L1 cache, which feeds the processor. See L1 cache, L2 cache and cache.

What is capacity miss?

Capacity misses occur when the cache is too small to hold all concurrently used data. Conflict misses are caused when several addresses map to the same set and evict blocks that are still needed.

What may be the reason of choosing directory based protocol over Snoopy bus protocol?

In a directory based scheme, participating caches do not broadcast requests to all other sharing caches of the block in order to locate cached copies, instead it queries the directory to retrieve the information about which block have cached copies and sends only to those particular processors and hence traffic saving …

What is coma in computer architecture?

Cache only memory architecture (COMA) is a computer memory organization for use in multiprocessors in which the local memories (typically DRAM) at each node are used as cache. This is in contrast to using the local memories as actual main memory, as in NUMA organizations.

Which directory protocol store n pointers where n is the number of processors in the system?

Directory pointers in a DirENB protocol encode binary processor identifiers, so each pointer requires LogiN bits of mem- ory, where N is the number of processors in the system.

Which is used to reduce cache hit time?

A hardware solution called anti-aliasing guarantees every cache block a unique physical address.

How can you improve cache memory performance by reducing cache hit time?

- Reducing the hit time – Small and simple first-level caches and way-prediction. …

- Increasing cache bandwidth – Pipelined caches, multi-banked caches, and non-blocking caches. …

- Reducing the miss penalty – Critical word first and merging write buffers.

Which of the basic cache optimization technique is used to reduce hit time?

– Direct-mapped caches can overlap the tag check with the transmission of the data, effectively reducing hit time. – Lower levels of associativity will usually reduce power because fewer cache lines must be accessed. conflict misses of 2-way SA cache?

What is RAM and ROM?

RAM, which stands for random access memory, and ROM, which stands for read-only memory, are both present in your computer. RAM is volatile memory that temporarily stores the files you are working on. ROM is non-volatile memory that permanently stores instructions for your computer.

Is cache and RAM disjoint?

(b) No, because cache and RAM are disjoint.

What are the 3 types of cache memory?

- direct-mapped cache;

- fully associative cache;

- N-way-set-associative cache.

What is cache updating?

About cache update subscriptions. Cache update subscriptions refresh the cache for the specified report or document. … For example, your system contains a set of standard weekly and monthly reports. These reports should be cached because they are frequently accessed.

What is consistent and coherent?

consistent – the quality of behaving in the same way over time. coherent – the quality of being logically connected.

Do you understand consistency and coherence?

Coherence is the quality of being local and orderly whereas consistency is the quality of being uniform. In writing, coherence refers to the smooth and logical flow of your writing and consistency refers to the uniformity of your style and content. This is the key difference between coherence and consistency.